NAND-Gatter

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

Ein NAND-Gatter (von englisch: not and – nicht und) ist ein Logikgatter mit zwei oder mehr Eingängen A, B, … und einem Ausgang Y, zwischen denen die logische Verknüpfung NICHT UND besteht. Ein NAND-Gatter gibt am Ausgang genau dann 0 aus, wenn alle Eingänge 1 sind. In allen anderen Fällen, d. h., wenn mindestens ein Eingang 0 ist, wird eine 1 ausgegeben.

Übersicht

| Funktion | Schaltsymbol | Wahrheitstabelle | Relais-Logik | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (vor 1976) | ||||||||||||||||||

|

|

|

| |||||||||||||||||

Die Schreibweise

entspricht dem Shefferschen

Strich.

Verwendung

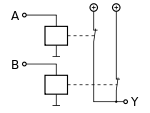

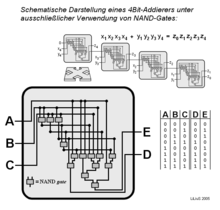

NAND-Gatter spielen in der Digitaltechnik die Rolle eines Standardbausteins, da sich allein mit ihnen alle logischen Verknüpfungen und somit auch komplexere Schaltungen (wie Addierer, Multiplexer usw.) zusammenstellen lassen, siehe auch vollständige Logiksysteme.

| Verknüpfung | Umsetzung |

|---|---|

| NOT x | x NAND x |

| x AND y | (x NAND y) NAND (x NAND y) |

| x NAND y | x NAND y |

| x OR y | (x NAND x) NAND (y NAND y) |

| x NOR y | ((x NAND x) NAND (y NAND y)) NAND ((x NAND x) NAND (y NAND y)) |

| x XOR y | (x NAND (y NAND y)) NAND ((x NAND x) NAND y) |

| ((x NAND y) NAND y) NAND ((x NAND y) NAND x) | |

| x XNOR y | (x NAND y) NAND ((x NAND x) NAND (y NAND y)) |

| ≡ x ⇔ y | |

| x ⇒ y | x NAND (y NAND y) |

| x ⇐ y | (x NAND x) NAND y |

| x ⇔ y | (x NAND y) NAND ((x NAND x) NAND (y NAND y)) |

| ≡ x XNOR y | |

| verum | (x NAND x) NAND x |

| falsum | ((x NAND x) NAND x) NAND ((x NAND x) NAND x) |

Realisierung

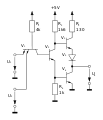

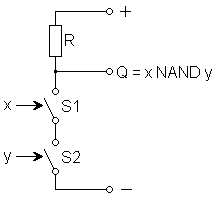

Die schaltungstechnische Realisierung erfolgt zum Beispiel mit zwei (oder entsprechend mehr) in Reihe geschalteten Schaltern (Transistoren), die den Ausgang Q auf Masse (logisch 0) legen, wenn sie alle eingeschaltet sind. Ist einer von ihnen aus, so ist die Masseverbindung unterbrochen und der Ausgang Q liegt auf Pluspotential (logisch 1).

Der NAND-Standardbaustein in Transistor-Transistor-Logik (TTL), als Vierfach NAND-Gatter mit der Bezeichnung 7400 ein bekannter Digital-IC, verwendet anstelle mehrerer Transistoren einen einzigen Transistor mit mehreren Emittern am Eingang. Diese speziellen Transistoren werden auch als Multiemitter-Transistor bezeichnet. Die Vorgängerlogik, die Diode-Transistor-Logik (DTL), verwendet statt des Multiemitter-Transistor mehrere Eingangsdioden zur Verknüpfung.

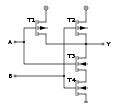

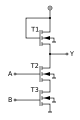

In der NMOS-Logik kann ein NAND-Gatter mit drei gleichwertigen n-Kanal-MOS-Feldeffekttransistoren (n-MOSFETs) mit weniger Chipfläche realisiert werden. Die gleichwertige Funktion ist auch in CMOS-Logik mit vier MOSFETs mit geringerer Leistung verfügbar: Liegt an Eingang A und B High-Potential, leiten T3 und T4, wobei T1 und T2 sperren. Somit liegt am Ausgang Y Low-Potential an. Bei allen anderen Eingangszuständen liegt High-Potential am Ausgang, weil T1 oder T2 leitet und gleichzeitig T3 und/oder T4 sperrt.

- Schaltungstechnische Realisierungen von NAND-Gattern in verschiedenen Logiken:

-

DTL

DTL -

NMOS

NMOS

© biancahoegel.de

Datum der letzten Änderung: Jena, den: 07.06. 2022