Und-Gatter

| Gatter-Typen | |

|---|---|

| NOT | |

| AND | NAND |

| OR | NOR |

| XOR | XNOR |

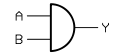

Ein Und-Gatter ist ein Gatter mit mehreren Eingängen und einem Ausgang, bei dem der Ausgang genau dann eine 1 liefert, wenn an allen Eingängen 1 anliegt. Es entspricht dem Logischen UND. In der Schaltalgebra wird die UND-Verknüpfung durch • (Mal), & oder ∧ dargestellt und wird auch als Konjunktion bezeichnet.

Übersicht

| Funktion | Schaltsymbol | Wahrheitstabelle | Relais-Logik | |||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| IEC 60617-12 | US ANSI 91-1984 | DIN 40700 (vor 1976) | ||||||||||||||||||

|

|

|

|

| ||||||||||||||||

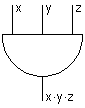

Und-Gatter mit größerer Anzahl von Eingängen

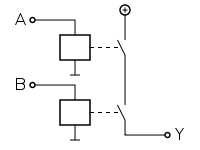

Ein Und-Gatter hat standardmäßig zwei Eingänge (AND2), jedoch stehen auch Und-Gatter mit mehr als zwei Eingängen im Handel zur Verfügung. Die untenstehende Abbildung zeigt ein Und-Gatter mit drei Eingängen (AND3).

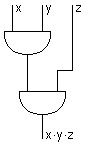

Darunter eine Schaltung für ein Und-Gatter mit drei Eingängen, die aus 2 Gattern mit jeweils 2 Eingängen realisiert wurde. Und-Gatter mit noch mehr Eingängen können in entsprechender Weise aufgebaut werden.

Auch wenn das Schaltsymbol kaum Aufschluss über den inneren Aufbau gibt, kann − bei Gatterfamilien, für die beide Darstellungsweisen verwendet werden − die untere als Hinweis auf ein ungünstigeres Laufzeitverhalten gewertet werden.

Ein Und-Gatter kann beispielsweise verwendet werden, um eine Maschine zu steuern: Die Maschine soll dann laufen, wenn beide Handkontakte UND beide Fußkontakte betätigt werden. Somit muss man 4 Signale verknüpfen, wofür ein UND-Gatter mit 4 Eingängen nötig ist (AND4).

Realisierung

UND-Gatter werden als integrierte Schaltung (IC) von vielen Herstellern produziert. Standardbausteine dieser Art sind z.B. unter der Bezeichnung „7408“ in TTL-Technik und als „74HC08“ in CMOS-Technologie erhältlich und beinhalten vier UND-Gatter mit jeweils zwei Eingängen. Die genaue Bauteilbezeichnung ist herstellerabhängig. Logik-Gatter dieser Art sind für wenige Cent im Elektronik-Fachhandel erhältlich.

CMOS

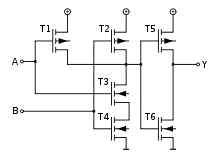

Das Bild rechts zeigt das Schaltbild eines Und-Gatters in CMOS-Technologie. Liegt an den Eingängen A und B High-Potential an, dann leiten T3 und T4, wobei T1 und T2 sperren. Dadurch liegt an T5 und T6 Low-Potential an und T5 leitet und T6 sperrt, weswegen am Ausgang Y High-Potential anliegt. Bei allen anderen Eingangszuständen liegt Low-Potential am Ausgang, weil T6 leitet.

© biancahoegel.de

Datum der letzten Änderung: Jena, den: 06.06. 2022