Arithmetisch-logische Einheit

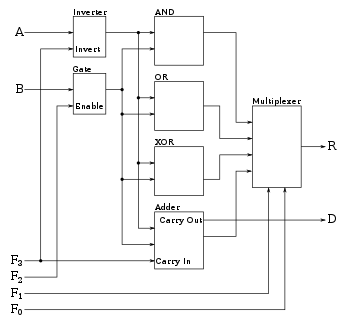

A Akkumulator, B Datenregister, F Funktion, D Statusausgabe, R Ergebnis (Result)

Eine arithmetisch-logische Einheit (englisch arithmetic logic unit, daher oft abgekürzt ALU) ist ein elektronisches Rechenwerk, welches in Prozessoren zum Einsatz kommt.

Funktionen

| F3 | F2 | F1 | F0 | R | |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 1 | A | |

| 1 | 0 | 0 | 1 | NOT A | |

| 0 | 1 | 0 | 0 | A AND B | |

| 0 | 1 | 0 | 1 | A OR B | |

| 0 | 1 | 1 | 0 | A XOR B | |

| 0 | 1 | 1 | 1 | A + B | |

| 1 | 1 | 1 | 1 | B – A |

Die ALU berechnet arithmetische und logische Funktionen. In älteren Prozessoren (bis etwa 8086) war sie außerdem für

- das Inkrementieren des Programmzählers zum Lesen von Befehlen,

- Berechnen von relativen Sprüngen (JR) und

- die Manipulation des Stackpointers (CALL, RET, PUSH, POP) und Adressberechnungen ([IX+n]) verantwortlich.

Sinnvollerweise kann sie mindestens folgende Minimaloperationen durchführen:

- Arithmetisch:

- Addition (ADD)

- Logisch:

- Negation (NOT)

- Konjunktion (Und-Verknüpfung, AND)

- Rechtsverschiebung oder -rotation (extrem aufwendig nachzubilden, im Gegensatz zur Rechtsverschiebung)

Typischerweise liegen jedoch auch noch zusätzlich folgende Operationen vor, die aber auch mittels der oberen drei auf Kosten der Rechenzeit (in mehreren Takten) nachgebildet werden können:

- Arithmetisch:

- Inkrement, Dekrement

- Addition mit Übertrag (ADC)

- Subtraktion (SUB)

- Subtraktion mit Übertrag (SBB)

- Vergleich (compare, CMP)

- Multiplikationen (MUL) mittels Multiplizierer

- Division

- Decimal adjust after addition (Dezimal-Angleichung nach Addition)

- Logisch:

- Disjunktion (Oder-Verknüpfung, OR)

- Kontravalenz (Exklusiv-Oder-Verknüpfung, XOR, EOR)

- Test-Befehl

- Rechts- und Linksverschiebung (Rechts-, Linksshift, ASR – arithmetische Shift rechts, ASL – arithmetische Shift links, LSR – logisches Verschieben nach rechts, LSL – logisches Verschieben nach links)

- Links- und Rechtsrotation (ROL, ROR)

- Register-Manipulationen und Bit-Veränderungen (Bits setzen, löschen und testen)

- Umsortieren von Bits und Bytes, AES-Befehle, CRC-Befehle

Alle ALUs verarbeiten Festkommazahlen. Gleitkommabefehle sind in vielen aktuellen CPUs mittlerweile Standard. Ausnahmen sind kleinere Mikrocontroller, die auf geringe Stromaufnahme oder auf geringe Herstellkosten getrimmt sind. Der Trend der letzten 15 Jahre ist es, ALUs auf Vektor-Verarbeitung umzustellen (Stand 2015).

Aufbau und Funktionsweise

Eine ALU kann zwei Binärwerte mit gleicher Stellenzahl (n) miteinander verknüpfen. Man spricht von n-Bit-ALUs. Typische Werte für n sind 8, 16, 32 und 64. Historisch erwähnenswert sind auch beispielsweise die 4-Bit-ALU 74LS181 und der 1-Bit-Prozessor MC14500B von Motorola. (Allerdings nennt sich die entsprechende Einheit darin lediglich LU (Logic Unit)). Begriffe wie 32-Bit- bzw. 64-Bit-CPU entstammen der Breite der Arbeitsregister der Prozessorarchitektur. Meist entspricht diese Breite auch der der ALU; mithin deuten diese Begriffe (32-Bit- bzw. 64-Bit-CPU) an, dass in entsprechenden Prozessoren auch ebensolche ALUs zum Einsatz kommen. Eine Ausnahme bildet hier beispielsweise der Z80, der mit einer 4-Bit-ALU arbeitet.

Die n-Bit ALU ist meist aus einzelnen 1-Bit-ALUs zusammengesetzt, die jeweils an die höherwertige ALU ein Carry-Bit weiterreichen, mit dem ein Übertrag an der jeweiligen Stelle gekennzeichnet wird. (Zur Beschleunigung werden häufig andere Verfahren (z. B. Carry-Look-Ahead) eingesetzt.) Um die zusammengeschalteten 1-Bit-ALUs in die geforderte Funktionsart umzuschalten, hat jede 1-Bit-ALU zusätzlich zu den Eingängen für die zu verknüpfenden Werte und das Carry-Bit noch einen Eingang für einen Steuervektor (Op.-Code); beim Einsatz in einem Prozessor werden diese Eingänge gemeinsam vom Steuerregister (Operationsregister, OR) des Prozessors versorgt.

Das Statusregister

Die gesamte n-Bit ALU hat außer dem Ausgangsvektor für das Ergebnis noch einen Bedingungsvektor, um ihren Zustand zu signalisieren. Beim Einsatz in einem Prozessor wird dieser Bedingungsvektor in dessen Statusregister (auch engl. condition code register) abgelegt.

Dieses Register enthält meistens vier Statusbits. Die einzelnen Werte des Statusregisters können von Maschinensprachebefehlen abgefragt werden und damit den weiteren Programmverlauf beeinflussen (z.B. bedingte Sprünge):

- Übertragsbit (C für engl. carry bit): Zeigt den Übertrag an, der bei Addition der n-ten Bits (der höchsten Stelle) der Operanden entsteht. Es wird als Kennzeichen für Bereichsüberschreitung bei Betrachtung des Ergebnisses als vorzeichenlose Zahl (nur positive Ergebnisse) verwendet. Wird in 2er-Komplement-Darstellung gerechnet (auch negative Zahlen möglich), so spielt das Carry-Bit für die Bereichsüberschreitung keine direkte Rolle.

- Überlaufbit (V für engl. overflow bit): Zeigt Zahlenbereichsüberschreitung bei 2er-Komplement-Rechnung an (Übertrag der zweithöchsten Stelle der Operanden). Weitere mögliche Bezeichnungen sind neben V noch OF oder O.

- Nullbit (Z für engl. zero bit): Zeigt an, ob das Ergebnis der vorhergehenden Rechenoperation Null ist (wird 1, wenn Inhalt des Akkumulatorregisters 0 ist).

- Negativbit (N): Wird gesetzt, wenn das Ergebnis der Operation als negative Zahl zu interpretieren sein kann (oberstes Bit des Akkumulatorregisters = 1).

Je nach ALU-Typ gibt es weitere Flags, zum Beispiel:

- Half carry bit (H): Zeigt einen Übertrag zwischen dem niederwertigen und höherwertigen Halbbyte an. Interessant für die Dezimalkorrektur bei der Umwandlung binärer Darstellung in BCD-Darstellung.

- Paritätsbit (P): Zeigt je nach Prozessor eine gerade bzw. ungerade Parität des Akkumulatorregisters an (Anzahl der Bits mit dem Wert 1 ist gerade bzw. ungerade).

Verwandte Systeme

Parallel Logic Units (PLUs) sind speziell auf Bitmanipulation zugeschnittene ALUs. Sie können parallel, also gleichzeitig mit anderen Rechenwerken auf die Daten zugreifen und sind deshalb über einen eigenen Datenpfad mit dem Arbeitsspeicher verbunden. PLUs sind Bestandteil einiger Signalprozessor-Typen, die als Hochgeschwindigkeits-Controller eingesetzt werden.

© biancahoegel.de

Datum der letzten Änderung: Jena, den: 13.06. 2024